本页面提供的是上一版软件的文档。当前版本中已删除对应的英文页面。

参数配置

Simulink® Design Verifier™ 分析的参数配置概述

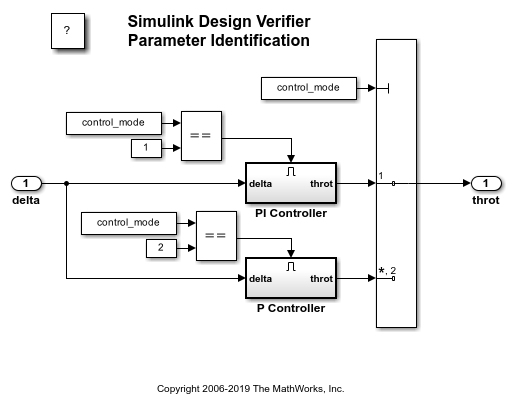

您可以指示 Simulink Design Verifier 在分析过程中考虑模型参数的除基础工作区或数据字典中设置的默认值之外的其他值。这使得 Simulink Design Verifier 可以在整个分析过程中将您的模型中的参数作为变量处理。参数配置定义了参数的允许值范围。

例如,假设某个模型包含一个 Switch 模块,该模块的默认值设置为 0,并且其控制端口受标定参数值 K 影响。K 的不同值会影响控制端口状态是被报告为死逻辑还是活动逻辑,并且会影响测试用例参数值。有关详细信息,请参阅在分析中使用参数配置。

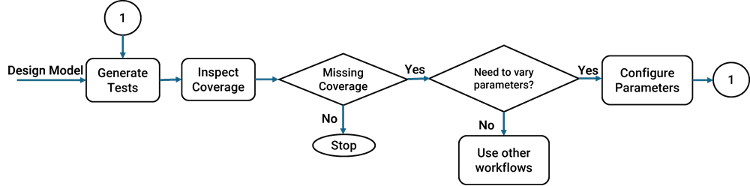

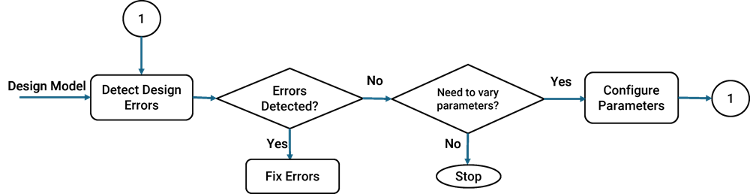

何时配置参数取决于您使用的工作流。

在为覆盖率生成测试用例时配置参数 - 在此工作流中,您在评估参数值是否影响模型覆盖率目标之后改变参数。

在设计错误检测分析期间配置参数 - 在此工作流中,您在检测设计错误以检查是否有任何参数值导致使用这些值的逻辑中出现运行时错误之后改变参数。

主题

参数配置的基础知识

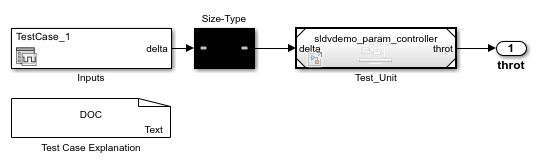

- 在分析中使用参数配置

Simulink Design Verifier 分析的参数配置概述。 - 创建 Simulink Design Verifier 分析的参数配置

在模型中配置参数以进行分析。 - 变体模块的参数配置

使用参数选择模型中的变体。 - 导入和导出参数约束

有关如何从参数表导入和导出指定参数约束的示例。

示例工作流

- 自动推断分析的参数规范

描述指定参数配置的工作流程。 - 从生成的代码中确定参数

描述指定参数配置的工作流程。 - 使用参数表查找约束

如何将参数指定为分析的变量的示例。 - 使用参数配置文件设置参数

描述如何在 MATLAB® 代码文件中定义参数配置。 - 指定结构或总线参数的参数配置

此示例描述了如何生成约束模型中的结构和总线信号值的测试。假设您的模型包含一个名为kpGainsStructure的变量,它是 MATLAB 工作区中的一个结构体。该模型使用 Bus Selector 模块将结构体字段分离为单独的总线信号。您可以约束结构体的值或总线信号的值,以确保它们在仿真期间保持在指定的范围内。 - 指定全面覆盖的参数配置

如何指定参数约束值以实现完整模型覆盖率的示例。