Simulink Design Verifier 分析基础知识

Simulink® Design Verifier™ 分析工作流简化了验证过程,并指导您完成从模型准备到结果解释的整个过程。使用 Simulink Design Verifier,您可以增强模型可靠性,缩短开发时间,并增加对系统设计的信心。

Simulink Design Verifier 工作流涉及准备要分析的 Simulink 模型或需求作为输入。

接下来,您将通过 Simulink Design Verifier 使用分析模式分析 Simulink 模型以执行以下操作:

生成实现模型覆盖率的测试用例。

检测运行时可能发生的设计错误。

证明属性并识别属性违规。

分析完成后,您可以查看结果以识别任何设计错误或验证模型属性。工作流的最后,您可以查看分析结果或导出结果以创建测试框架。

本教程中的工作流侧重于 Simulink Design Verifier 分析步骤。

检查模型兼容性

在 Simulink Design Verifier 分析模型之前,软件会检查模型是否兼容并适合进行分析。有关模型兼容性的详细信息,请参阅检查模型兼容性以进行分析。软件会对您的模型运行兼容性检查,然后创建模型表示。模型表示包含您可以在分析过程中使用的模型工件。兼容性检查会向您说明模型是完全兼容、部分兼容还是不兼容。

Simulink 支持模型中的广泛软件功能,但 Simulink Design Verifier 不支持其中一些功能。有关详细信息,请参阅Simulink Design Verifier 中支持和不支持的 Simulink 模块和Simulink Design Verifier 对 Simulink 软件功能的支持限制。

应用模块替换规则

如果要解决模型中的兼容性限制或自定义模型元素以进行分析,您可以使用 Simulink Design Verifier 模块替换规则。有关详细信息,请参阅什么是模块替换?和不受支持的模块的模块替换。

如果要在分析过程中为模型中的参数生成其他值,可使用 Simulink Design Verifier 参数配置。有关详细信息,请参阅在分析中使用参数配置。

设置 Simulink Design Verifier 选项

您可以在“配置参数”对话框中设置 Simulink Design Verifier 分析选项。您也可以使用 sldvoptions 函数在命令行中指定 Simulink Design Verifier 选项。有关详细信息,请参阅设置 Simulink Design Verifier 分析选项。

对模型执行分析

您可以对模型进行以下分析:

设计错误检测:检测运行时可能发生的设计错误。有关详细信息,请参阅分析模型以检测设计错误。

测试用例生成:生成实现模型覆盖率的测试用例。有关详细信息,请参阅。

属性证明分析:证明属性并识别属性违规。有关详细信息,请参阅证明模型属性的工作流。

如果您计划生成测试用例或证明模型中的属性,请首先运行用于检测整数溢出和除以零的设计错误检测。有关详细信息,请参阅以下主题:

生成分析结果

Simulink Design Verifier 完成对模型的分析后,会在“结果摘要”窗口中显示分析要点和结果选项。有关详细信息,请参阅对模型执行分析。

解释分析结果

您可以查看分析结果并生成 HTML、DOCX 或 PDF 格式的分析报告。有关详细信息,请参阅查看分析结果。

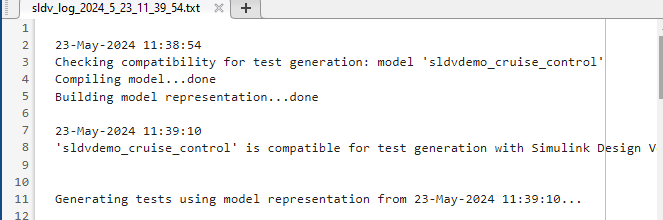

您每次分析模型时,Simulink Design Verifier 都会创建一个日志文件。

要查看日志文件,请点击 Simulink Design Verifier 日志窗口中的查看日志。

日志文件以 .txt 格式生成,并且不属于当前区域设置的字符在日志文件中会显示为乱码。

日志文件包含模型中每个对象的分析结果列表。日志文件的内容与分析过程中日志窗口中显示的分析结果相对应。