Simulink Real-Time FPGA I/O 模块

您可以生成 FPGA 编程文件和 Simulink Real-Time FPGA I/O 接口以在 Speedgoat® I/O 模块上部署。请参阅IP Core Generation Workflow for Speedgoat Simulink-Programmable I/O Modules。

类

函数

主题

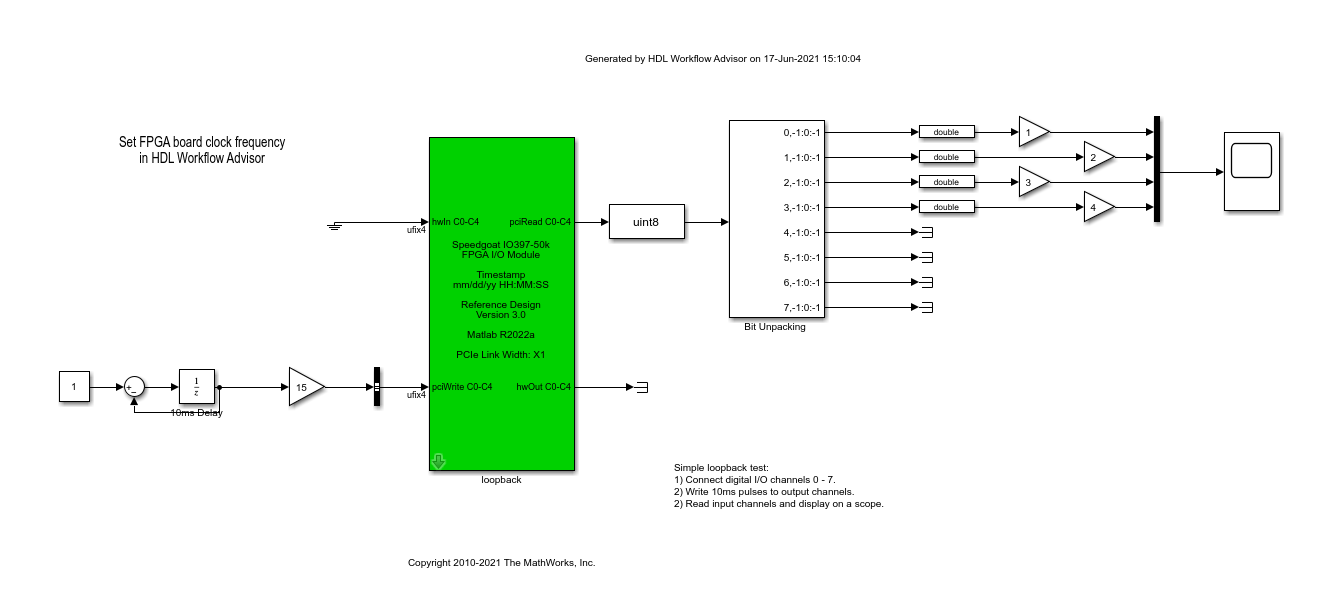

- IP Core Generation Workflow for Speedgoat Simulink-Programmable I/O Modules

Use the IP Core Generation workflow with Speedgoat I/O modules and embed the IP core into the reference design.

- Program Target FPGA Boards or SoC Devices

How to program the target Intel or Xilinx Hardware.

- Generate Simulink Real-Time Interface Subsystem for Simscape Two-Level Converter Model

Generate HDL code and Simulink Real-Time interface model from Simscape™ models.

- Speedgoat FPGA Support with HDL Workflow Advisor

Implementing Simulink algorithms on FPGAs on board Speedgoat FPGA I/O modules.

- Map Bus Data Types to PCIe Interface

When you use bus data types at the DUT interface ports, you can directly map the interface ports to PCIe interfaces.

疑难解答

Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.