Simulink Design Verifier

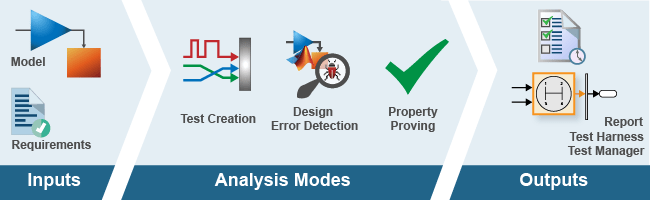

Simulink® Design Verifier™ 使用形式化方法来识别模型中隐藏的设计错误。它可以检测模型中导致整数溢出、死逻辑、数组访问违规和除以零的模块。它可以通过形式化方式验证设计是否满足功能需求。对于每个设计错误或需求违规,它都会生成一个用于调试的仿真测试用例。

Simulink Design Verifier 可为模型覆盖率和自定义目标生成测试用例,以扩展基于需求的现有测试用例。这些测试用例可驱动您的模型满足条件、决策、修正条件/决策 (MCDC) 和自定义覆盖率目标。除覆盖率目标之外,您还可以指定自定义测试目标以自动生成基于需求的测试用例。

对行业标准的支持可通过 IEC Certification Kit (for IEC 61508 and ISO 26262) 和 DO Qualification Kit (for DO-178) 获得。

Simulink Design Verifier 快速入门

Simulink Design Verifier 基础知识学习

准备和分析模型

识别用于单元或系统级测试的可分析组件,解决模型不兼容或分析超时问题

检测并消除 Bug

检测运行时错误和逻辑错误,调试设计中的问题

指定并验证设计需求

根据需求验证设计,使用输入假设优化反例

生成测试

生成测试用例集以实现模型和代码覆盖率并满足自定义测试准则

测试模型等效性

测试模型和生成代码的行为等效性,或是模型在不同 Simulink 版本中运行时的行为等效性

查看分析结果

记录和查看分析结果,生成报告,检查测试用例

工具鉴定与认证

针对 IEC 认证鉴定 Simulink Design Verifier