FPGA、ASIC 和 SoC 开发

从算法开发到硬件设计和验证,实现工作流全程自动化

使用 MATLAB® 和 Simulink® 开发原型和生产应用程序,以部署在 FPGA、ASIC 和 SoC 设备上。借助 MATLAB 和 Simulink,您可以:

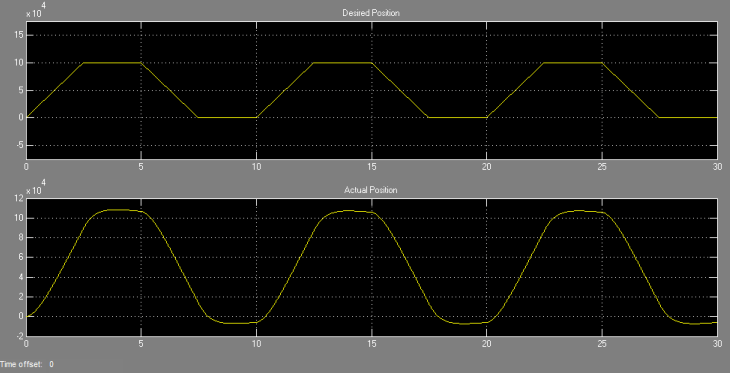

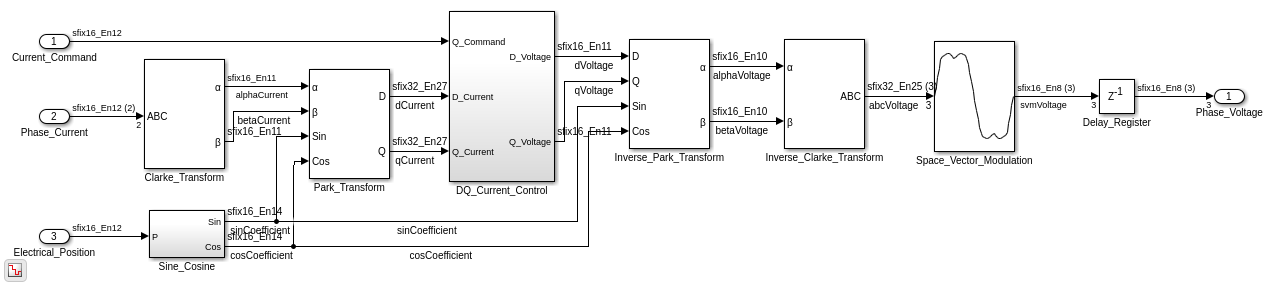

在高度抽象级别对数字、模拟和软件进行建模和仿真。

使用自动向导进行定点转换,或者为任意目标设备生成原生浮点运算。

通过内存、总线和 I/O 建模对硬件和软件架构进行分析。

生成经过优化、可读且可跟踪的 VHDL®、Verilog® 或 SystemVerilog,用于在数字逻辑中实现。

生成针对处理器优化的 C/C++ 代码,以部署到嵌入式处理器。

对连接到 MATLAB 或 Simulink 测试平台的 HDL 仿真器或 FPGA 或 SoC 设备上运行的算法进行验证。

适用产品: FPGA、ASIC 和 SoC 开发

主题

建模和仿真

- Use Simulink Templates for HDL Code Generation (HDL Coder)

Use Simulink model templates for HDL code generation to create efficient hardware designs. - Transmit and Receive Tone Using AMD RFSoC Device - Part 1 System Design (SoC Blockset)

Design and simulate data path using SoC Blockset™ on Xilinx® RFSoC device. - Wireless Communications Design for ASICs, FPGAs, and SoCs (HDL Coder)

Design wireless communication algorithms for hardware by using Wireless HDL Toolbox™ blocks. - Implement Digital Downconverter for FPGA (DSP HDL Toolbox)

Design a digital downconverter (DDC) for LTE on FPGAs. - HDL OFDM Receiver (Wireless HDL Toolbox)

Implement OFDM-based wireless receiver optimized for hardware. - Convert MATLAB Vision Algorithm to Hardware-Targeted Simulink Model (Vision HDL Toolbox)

Create a hardware-targeted design in Simulink that implements the same behavior as a MATLAB reference design.

验证

- Get Started with Simulink HDL Cosimulation (HDL Verifier)

Set up an HDL Verifier™ application using the Cosimulation Wizard in the Simulink® environment. - FPGA-in-the-Loop Simulation (HDL Verifier)

FPGA-in-the-loop (FIL) simulation provides the capability to use Simulink or MATLAB software for testing designs in real hardware for any existing HDL code. - Data Capture Workflow (HDL Verifier)

Capture signal data from a design running on an FPGA. - Access FPGA Memory Using JTAG-Based AXI Manager (HDL Verifier)

Use JTAG-based AXI manager to access memories connected to an FPGA. - UVM Component Generation Overview (HDL Verifier)

Generate a Universal Verification Methodology (UVM) environment from a Simulink model. - Generate SystemVerilog DPI Component (HDL Verifier)

Generate a DPI component from Simulink, and explore various configuration parameters. - Verify Generated Code Using HDL Test Bench from Configuration Parameters (HDL Coder)

Generate a HDL test bench to simulate and verify the generated HDL code for your design.

代码生成和部署

- Basic HDL Code Generation Workflow (HDL Coder)

Follow the workflow for HDL code generation and FPGA synthesis from MATLAB and Simulink algorithms. - Generate IP Core with AXI-Stream Interface (HDL Coder)

Use the AXI4-Stream interface to enable high speed data transfer between the processor and FPGA on Zynq® hardware. - Custom IP Core Generation (HDL Coder)

Generate a custom IP core from a model or algorithm using the HDL Workflow Advisor. - Targeting FPGA & SoC Hardware Overview (HDL Coder)

High-level steps for targeting an FPGA or SoC platform. - Transmit and Receive Tone Using AMD RFSoC Device - Part 2 Deployment (SoC Blockset)

Implement and verify design using SoC Blockset on Xilinx RFSoC device. - Prototype Deep Learning Networks on FPGA and SoC Devices (Deep Learning HDL Toolbox)

Accelerate the prototyping, deployment, design verification, and iteration of your custom deep learning network running on a fixed bitstream by using thedlhdl.Workflowobject.