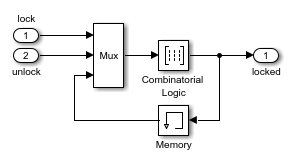

Memory

输出上一个时间步的输入

库:

Simulink /

Discrete

HDL Coder /

Discrete

描述

Memory 模块将其输入保持并延迟一个主积分时间步。当放置于迭代子系统中时,该模块将其输入保持并延迟一个迭代。此模块接受连续和离散信号。此模块接受一个输入并生成一个输出。每个信号可以是标量、向量、矩阵或 N 维数组。如果输入为非标量,该模块会将输入的所有元素保持并延迟相同的时间步。

使用初始条件参数指定第一个时间步的模块输出。仔细选择此参数可以最大程度地减少不需要的输出行为。但是,您不能指定采样时间。此模块的采样时间取决于所用求解器的类型,您也可以指定继承采样时间。继承采样时间参数确定采样时间是继承的还是基于求解器。

提示

当以下两个条件均为真时,避免使用 Memory 模块:

型使用变步长求解器

ode15s或ode113。模块的输入在仿真期间发生变化。

当 Memory 模块继承离散采样时间时,该模块类似于 Unit Delay 模块。但是,Memory 模块不支持状态记录。如果需要记录最终状态,请改用 Unit Delay 模块。

与类似模块的比较

Memory、Unit Delay 和 Zero-Order Hold 模块提供相似的功能,但各自具有不同的能力。此外,每个模块的用途也各不相同。

下表显示每个模块的推荐用途。

| 模块 | 模块的用途 | 引用示例 |

|---|---|---|

| Unit Delay | 使用您指定的离散采样时间实现延迟。该模块接受并输出具有离散采样时间的信号。 |

|

| Memory | 将信号延迟一个主积分时间步。在理想情况下,该模块接受连续(或在子时间步中固定)的信号并输出在子时间步中固定的信号。 |

|

| Zero-Order Hold | 将具有连续采样时间的输入信号转换为具有离散采样时间的输出信号。 |

每个模块有以下功能。

| 功能 | 内存 | 单位延迟 | 零阶保持 |

|---|---|---|---|

| 指定初始条件 | 是 | 是 | 否,因为在时间 t = 0 的模块输出必须与输入值相匹配。 |

| 指定采样时间 | 否,因为该模块只能从驱动模块或用于整个模型的求解器继承采样时间。 | 是 | 是 |

| 支持基于帧的信号 | 否 | 是 | 是 |

| 支持状态记录 | 否 | 是 | 否 |

总线支持

Memory 模块支持总线。输入可以是满足下列限制条件的虚拟或非虚拟总线信号:

初始条件必须为零、非零标量或有限数值结构体。

如果初始条件为零或结构体,而您指定了状态名称,则输入不能是虚拟总线。

如果初始条件为非零标量,则不能指定状态名称。

有关指定初始条件结构体的信息,请参阅Specify Initial Conditions for Bus Elements。

Memory 模块的非虚拟总线输入中的所有信号都必须具有相同的采样时间,即使关联总线对象的元素指定继承采样时间也是如此。您可以使用 Rate Transition 模块更改总线中单个信号或所有信号的采样时间。有关详细信息,请参阅Modify Sample Times for Nonvirtual Buses和支持总线的模块。

可使用总线数组作为 Memory 模块的输入信号。可为初始条件参数指定:

值

0。在这种情况下,总线数组中的所有单个信号都使用初始值0。结构体数组,为总线数组中的每个信号指定初始条件。

标量结构体,为总线类型定义的每个元素指定初始条件。使用此方法可为数组中的每条总线指定相同的初始条件。

有关定义和使用总线数组的详细信息,请参阅使用总线数组组合非虚拟总线。

示例

扩展示例

端口

输入

输出

参数

模块特性

扩展功能

版本历史记录

在 R2006a 之前推出另请参阅

主题

- 模型接口元素的 C 数据代码接口配置 (Simulink Coder)

- 使用 Struct 存储类将参数数据组织为结构体 (Embedded Coder)

- 数据对象