Simulink Cosimulation

Cosimulate HDL code with Simulink®

To get started, see Verify HDL Module with Simulink Testbench.

Blocks

| HDL Cosimulation | Cosimulate HDL design by connecting Simulink with HDL simulator |

| To VCD File | Generate value change dump (VCD) file |

Apps

| HDL Verifier | Generate HDL verification artifacts and follow verification workflows from a Simulink subsystem |

| Cosimulation Wizard | Generate a cosimulation block or System object from existing HDL files |

Functions

Objects

cosimulationConfiguration | Configure HDL cosimulation workflow (Since R2022b) |

Topics

Startup and Connection

- Set Up for HDL Cosimulation

To cosimulate your HDL code with a MATLAB® or Simulink design, you must first: - Supported EDA Tools and Hardware

List of supported third-party EDA software and FPGA boards. - Start HDL Simulator for Cosimulation in Simulink

Set up the connection between the HDL simulator and Simulink. - TCP/IP Socket Ports

Provides some direction for choosing TCP/IP socket ports. - Cross-Network Cosimulation

Provides instructions for performing cosimulation across a local network.

Testbench

- Get Started with Simulink HDL Cosimulation

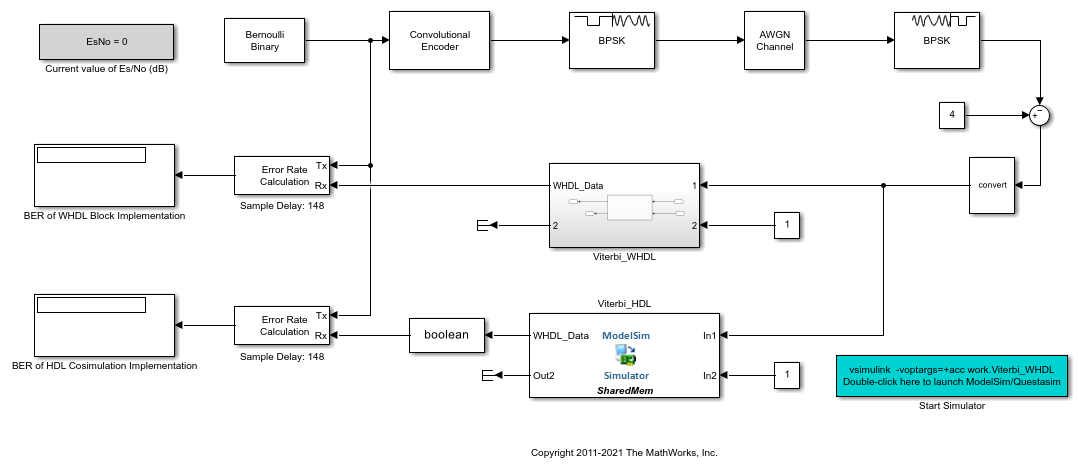

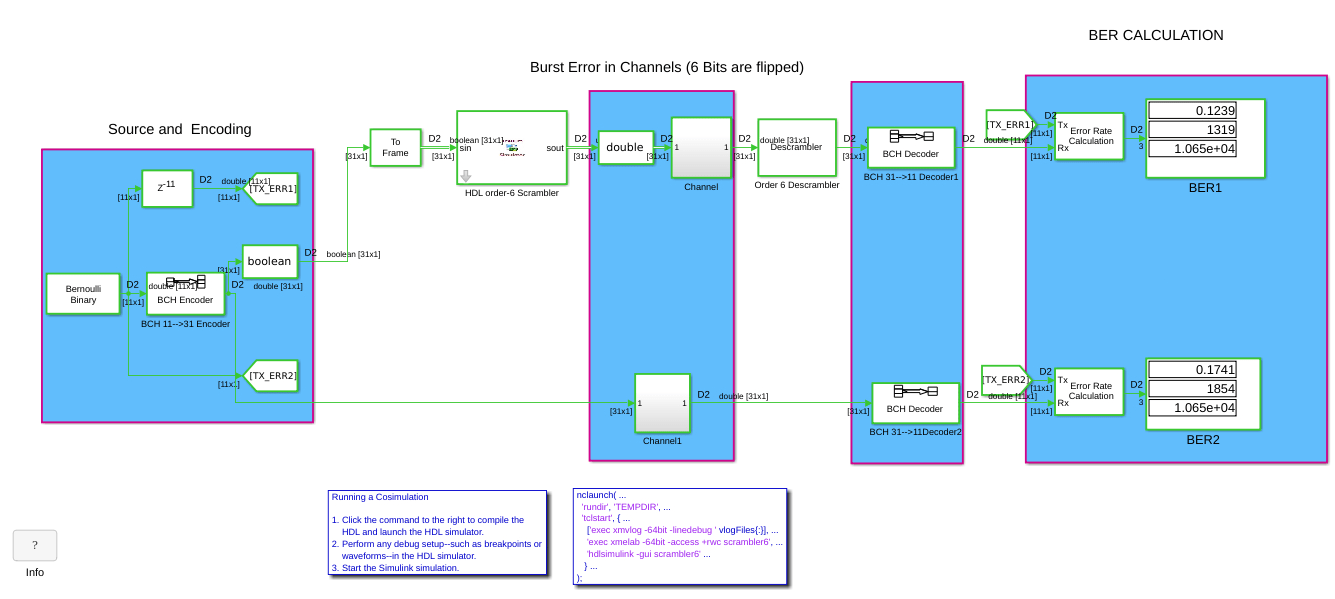

Set up an HDL Verifier™ application using the Cosimulation Wizard in the Simulink® environment. - Simulink as a Testbench

Provides an introduction to the process for integrating HDL Verifier™ blocks into a Simulink design. - Create a Simulink Cosimulation Testbench

The steps to code and run a Simulink-as-testbench cosimulation for use with the HDL Verifier software. - Verify HDL Module with Simulink Testbench

Set up an HDL Verifier session that uses Simulink to verify a simple VHDL® model.

Verification of Generated HDL Code with Cosimulation Testbench (requires HDL Coder license)

- Generate Test Bench and Enable Code Coverage Using the HDL Workflow Advisor (HDL Coder)

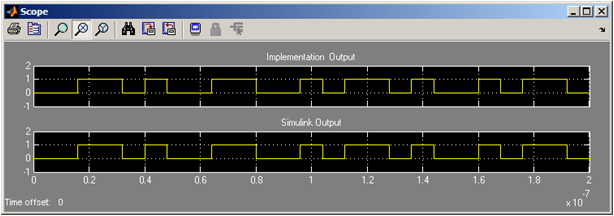

Generate test bench and code coverage for generated HDL code using the HDL Workflow Advisor. - Automatic Verification of Generated HDL Code from Simulink

Verify generated HDL code using a generated cosimulation model.

Component Algorithm

- Component Simulation with Simulink

Provides an introduction to the process for integrating blocks into a Simulink design. - Create Simulink Model for Component Cosimulation

Provides a high-level view of the steps involved in coding and running a Simulink-as-component cosimulation for use with the software.

Cosimulation with Simulink

- HDL Cosimulation

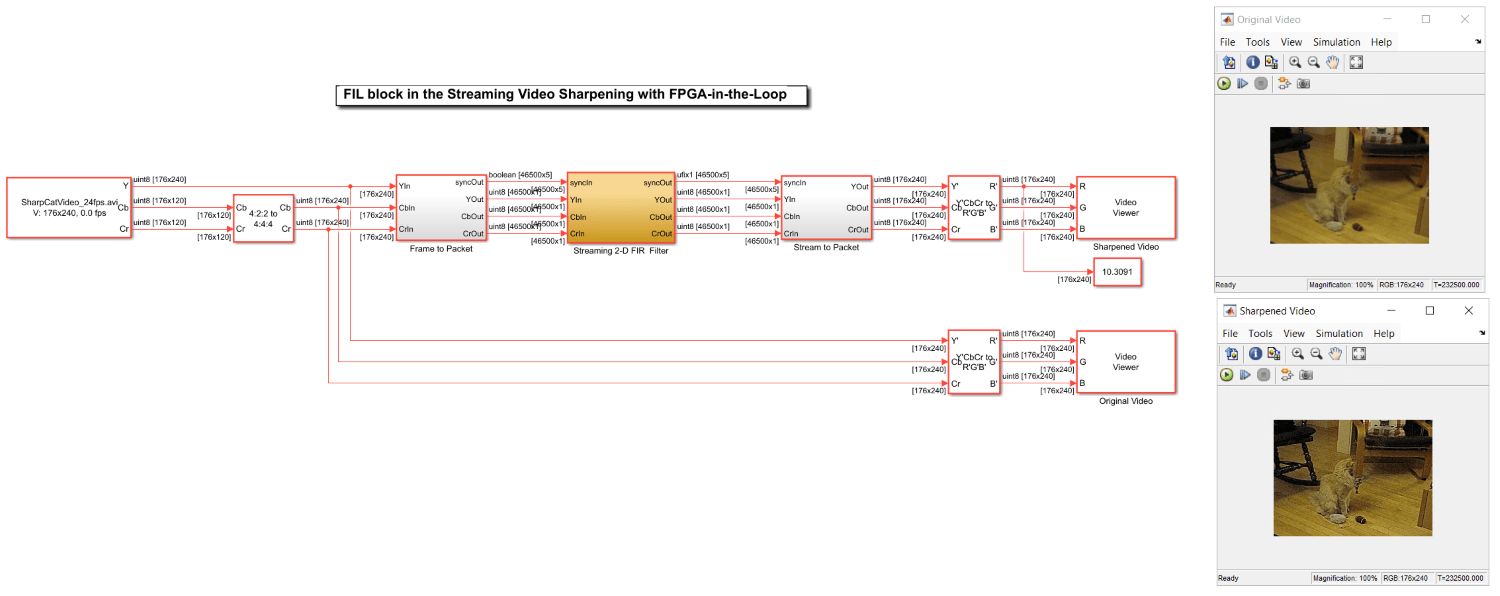

The HDL Verifier software consists of MATLAB functions, a MATLAB System object™, and a library of Simulink blocks, all of which establish communication links between the HDL simulator and MATLAB or Simulink. - Performing Cosimulation

Next steps after you generate a function or block representing your HDL module. - Prepare to Import HDL Code for Cosimulation

Prepare for cosimulation and choose whether to cosimulate your HDL code as a function, System object, or block. - Import HDL Code for HDL Cosimulation Block

Generate a Simulink block to cosimulate your HDL code. - Run a Simulink Cosimulation Session

Run your testbench or algorithm, including the cosimulation of your HDL module. - Relocate HDL Cosimulation Design Support Files

Relocate your HDL Cosimulation design support files for model sharing. - Use HDL Parameters in Cosimulation

Use Verilog parameters or VHDL generics in cosimulation.

HDL Simulator Interaction

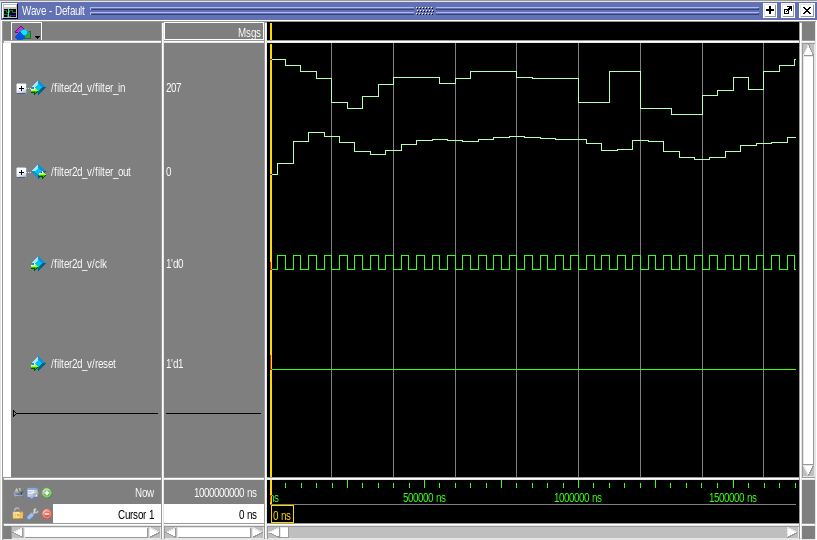

- Simulation Timescales

The representation of simulation time differs significantly between the HDL simulator and Simulink. - Clock, Reset, and Enable Signals

You can create rising-edge or falling-edge clocks, resets, or clock enable signals that apply internal stimuli to your model under cosimulation. - Simulation Speed Improvement Tips

Provides suggestions for optimizing your cosimulation performance. - Frame-Based HDL Cosimulation

Frame-Based processing for HDL Cosimulation. - Supported Data Types

If your HDL application needs to send HDL data to a MATLAB function or a Simulink block, you may first need to convert the data to a type supported by MATLAB and the HDL Verifier software. - Race Conditions in HDL Simulators

Describes ways to avoid race conditions in hardware cosimulations with MATLAB and Simulink software.

Recording Signal State Transitions for Post-Processing

- Add a Value Change Dump (VCD) File

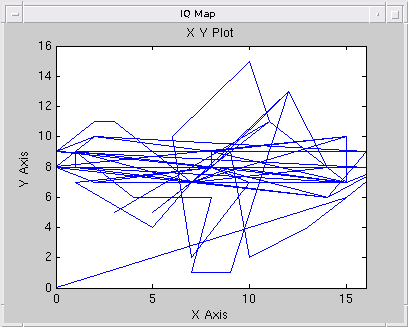

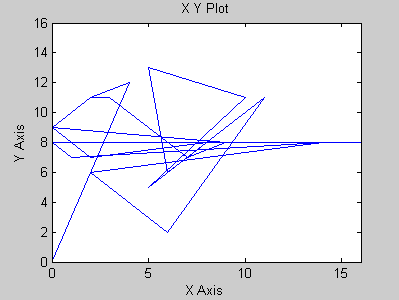

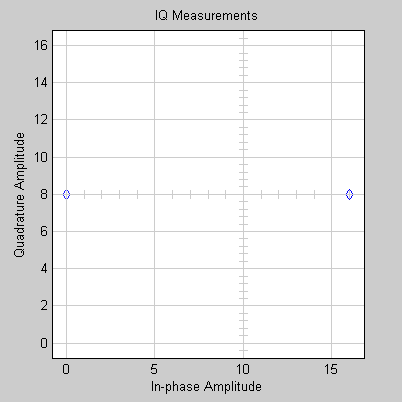

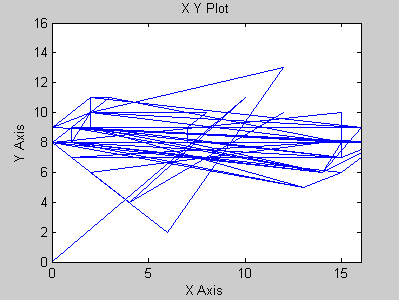

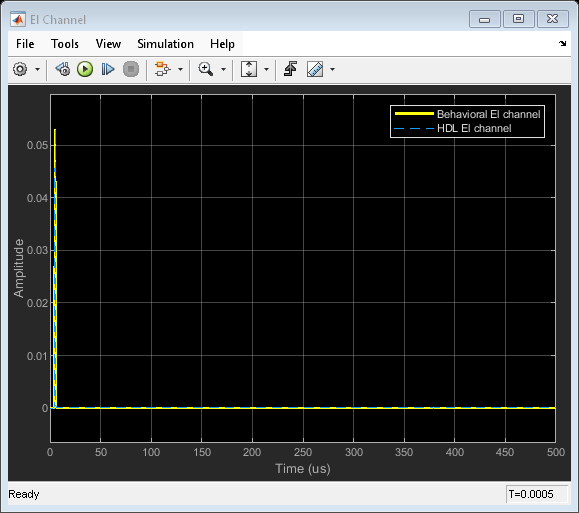

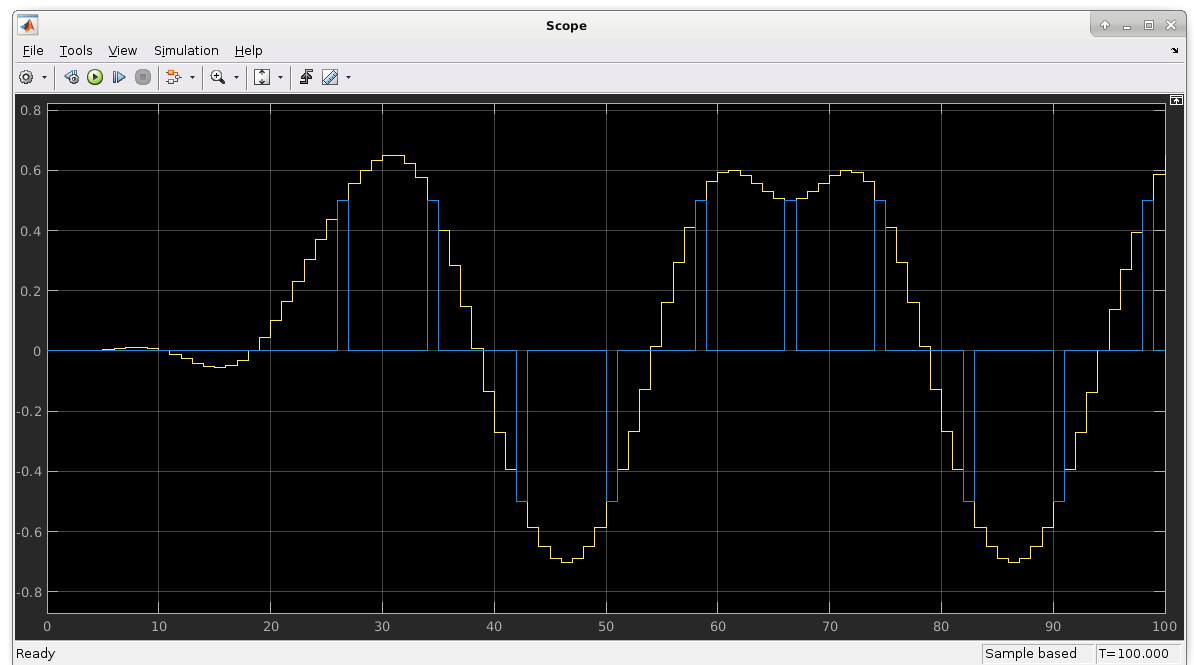

A value change dump (VCD) file logs changes to variable values, such as the values of signals, in a file during a simulation session. - Visually Compare Simulink Signals with HDL Signals

Guides you through the basic steps for adding a To VCD File block to a Simulink model for use with cosimulation.