准备和分析模型

识别用于单元或系统级测试的可分析组件,解决模型不兼容或分析超时问题

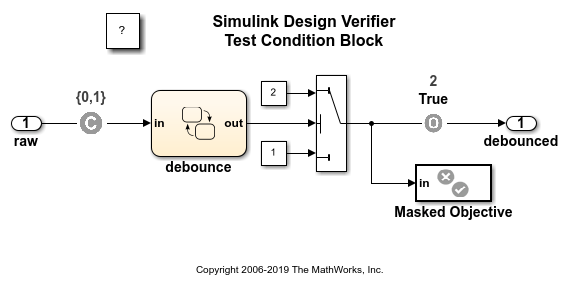

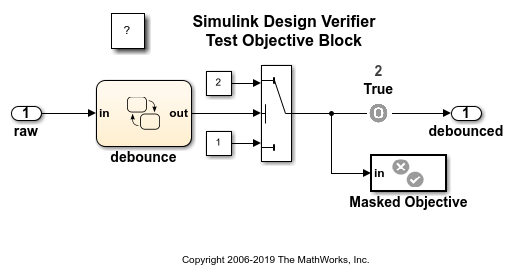

在构建模型时,使用 Simulink® Design Verifier™ 来指导设计过程。在更新模型时,通过迭代运行分析来避免潜在的 Bug。如果 Simulink 中已存在现有设计,请配置设计的相应部分以进行 Simulink Design Verifier 分析。

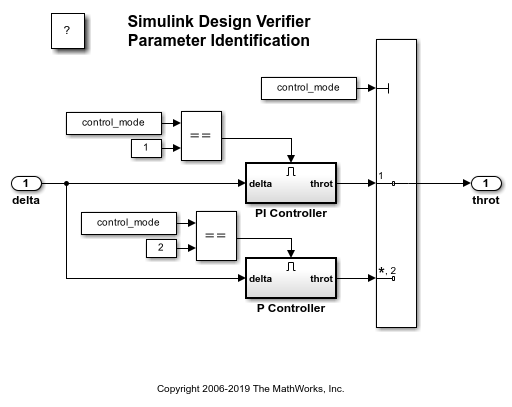

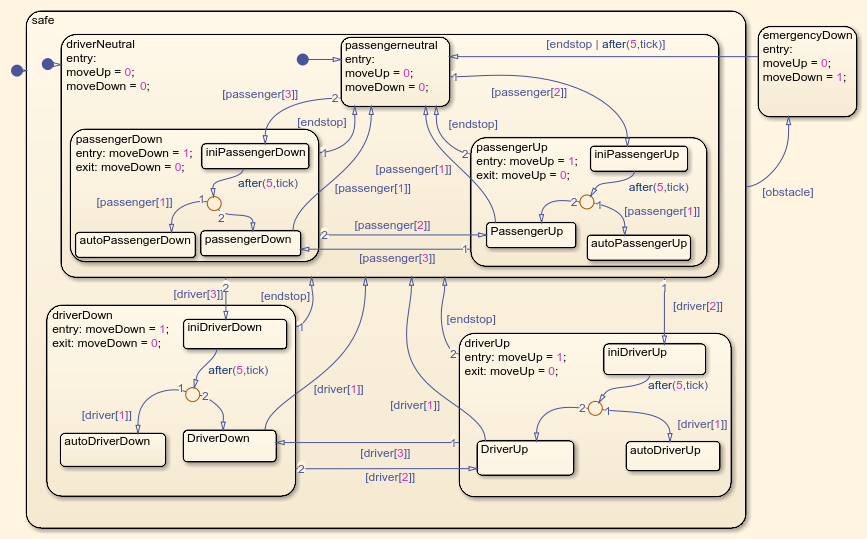

如果 Simulink 中已存在现有模型、子系统或子图,请配置设计的相应部分以进行 Simulink Design Verifier 分析。对于大型或复杂模型,应采用自下而上的方法(首先分析较小的组件)以获得最佳结果。

类别

- 分析模型或子系统

准备用于分析的模型或子系统,运行分析

- 消除模型不兼容或分析超时问题

调整模型、模型参数或分析选项以更好地分析模型

- 参数配置

Simulink Design Verifier 分析的参数配置概述

- 降低模型复杂度

使用自下而上的方法分析大型模型,定义模块替换规则

- Simulink Design Verifier 分析的最佳做法

Simulink Design Verifier 分析的最佳做法、注意事项和支持限制